권찡's 공학이야기

회로이론 - amplifier(이상적인 opamp) 본문

회로에서 가장 기본이 되는 소자는 RLC입니다. 저항, 인덕터, 커패시터 입니다.

그러나 다른 소자를 하나 소개하고 넘어가겠습니다. 정말 기본개념 정도로만 짚고 넘어갈 것입니다. 이 opamp는 자세한 내용은 전자회로에 들어가면 더 자세히 배울 것입니다.

opamp 소자 중에 아마 대학 내용으로 많이 나오는 소자는 LM741이 아닐까 하네요.

생긴건 직육면체 같이 생겼습니다. 내부에는 저 삼각형 같은 회로가 있다고 보시면 됩니다. 이런 opamp는 회로도를 그릴때 아래와 같이 표기합니다.

이제 막 회로이론을 배우는 분들은 실제 amp의 동작을 이해하기에는 무리가 있습니다. 때문에 이상적인 apamp를 먼저 배우도록 하겠습니다.

기본적으로 opamp는 차동 증폭기 입니다

무슨소리냐 하면 -단자에 들어오는 전압과 +단자에 들어는 전압의 차이를 증폭시키는 것이죠

증폭시킬때 gain 이 있는데 증폭률을 말하는 것입니다. A를 증폭률이라고 해보죠.

즉 V(out) = A(Vin+ - Vin-)로 증폭시키는 것입니다.

회로상 크게보면 opamp를 하나의 node로 보고 해석해도 무방합니다.

즉

5개의 선이 곂쳐지는 node로 보면 KCL이 적용됩니다.

이런 이상적인 opamp는 선형적 그리고 비선형적 으로 동작합니다.

선형적으로 동작하는 구간에서 앰프는 3가지 조건을 만족합니다

1) |Vo| < Vsat(최대전압)

2) |io| < i sat(최대전류)

3) |dvo(t)/dt| < SR(슬루율:slew rate)

즉 만약에 최대 전압이 14V라면 아무리 증폭시켜도 14V를 넘을수 없다는 것이지요. 증폭시켜도 최대전류치를 넘을수 없다는 것입니다. 슬루율은 지금은 넘어가겠습니다. 회로이론 막 시작한 사람이 설명해도 알아먹기 힘들것입니다.

회로해석에 있어서 이상적인 opamp는 3가지만 기억하면됩니다.

1. - input 으로 들어오는 전류는 0이다

2. +input으로 들어오는 전류는 0이다

3. - input 과 +input의 전압은 같다

위 3가지를 앰프의 3가지 조건에 대입하면

input impedence 가 무한대

outout impedence 가 0

gain 이 무한대

가 됩니다. 이상적인 조건이지요. 임피던스는 간단히 저항이라고 기억하고 넘어가죠.

실제 조건은 다르지만 본 장에서는 이상적인 앰프를 다루겠습니다.

예를 들어 opamp를 활용한 회로를 한법 봅시다.

이 회로를 보면서 알아보죠

여기서 i N 과 i p 전류가 0라는 것이고

Vp 와 Vn 이 같다

라는것을 알수가 있습니다. 왜냐하면 이상적인 opamp의 조건은 input 단에 들어오는 전류는 0이며, input단의 node voltage는 같기 때문이죠.

입력쪽에 전압및 전류를 signal로 본다면 이 신호가 증폭되는 구조이죠

이제 gain 에 대해 알아보도록 하겠습니다.

gain 반전 증폭기냐 비반전 증폭기냐에 따라서 gain에 달라질수 있죠

반전증폭기란 입력 신호가 opamp의 -단에 달린 증폭회로입니다

이렇게 입력 전압이 -단에 달려있는것을 말하죠

즉 V(out) = A[(Vin+) - (Vin-)]

A값이 negative 값을 가진다는 것이죠

이때 이득(gain)값은 피드백 저항 즉 Rf값을 통해 조절할수 있습니다.

지금까지 배운 내용으로 간단히 이 회로를 분석할 수 있습니다.

연산 증폭기의 특징인 입력단자 V+와 V-에 흘러들어가는 입력 전류는 0

전압은 같습니다.

따라서 Rin 저항과 Rf저항에 흐르는 전류는 같죠

그림에서 저항사이에 node에 KCL을 적용하면

이 됩니다 이때의 이득은

이 되는 것이죠

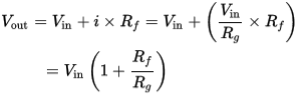

비반전 증폭기의 경우 역시 마찬가지입니다.

Vin이 +단자에 달려있으므로 이득은 양의 값을 취합니다.

기본적인 조건하에

Rg에 흐르는 전류를 구해보죠

i = Vin/Rg 입니다.(-단에 전압은 +단의 전압과 같기때문에)

이때 이득을 구해보겠습니다.

이러한 연산증폭기의 응용 회로는 이외에도 여러가지가 있습니다.

이번에는 다른 응용회로를 다뤄보죠.

이러한 응용회로의 기본 구조를 알고 있다면 회로해석에 있어서 빠르게 나뉘어 회로해석을 할수 있죠

차근차근 하나씩 다루겠습니다.

첫번째 는 voltage follower 즉 buffer amplifier입니다

이러한 회로를 buffer amp라고 합니다. 피드백으로 저항이 연결되어있지 않은 형태로 이득값은 1이 되어 입력이 10볼트가 들어가 출력이 10볼트가 되는 것입니다.

어차피 그대로 나오는데 왜 버퍼를 사용하는지 궁금해 하시는 분들도 있을거라고 생각합니다.

그 이유는 이전에 설명드린것처럼 opamp는 매우 높은 입력 임피던스를 가지고 있습니다.

그렇기에 매우 적은 전류가 회로에서 흘러나오게 되는 것입니다.

즉 이런 버퍼는 전압은 유지시키되 전류를 매우 약하게 나오게 하는것이죠 이런 역활로 매우 많은 전류가 흘러 회로가 박살나는 것을 방지 할수 있습니다.

쉽게 말해 출력의 안정화를 위해서죠

2번째 는 전압 덧셈기입니다.

각각의 입력신호가 -단에 달려있으니 이득은 -가 되겠고

각 저항이 입력에 달려있는 형태입니다

이때 Vout은 밑의 식으로 정의 됩니다

이때 만약 모든 저항값이 동일하다면 전부 약분되어서

가 되어 전압을 덧셈할수 잇는것이죠

3번째 다룰 응용회로는 차동증폭기입니다. 이증폭이 말그대로 +, -단의 전압차를 이용해서 증폭시키는 회로죠

이런식으로 회로를 구성하는 것으로 우리는 차동증폭을 할수있습니다.

출력은

으로 이뤄집니다.

4번째는 converter로 변환기 라고도 합니다

다룰것은 current to voltage converter로

전류가 어느정도 들어가느냐에 따라서 전압을 다르게 출력하는 회로입니다.

다양한 응용회로가 존재하지만 처음에 배운 opamp의 조건을 알고 계신다면 해석이 가능하죠

이런 opamp 응용회로는 인덕터나 커패시터를 추가하여 더 다양한 회로로 사용가능합니다.

지금은 회로이론에서 앞으로 배울 내용에 대한 개론이라 보시고 나중에 더 깊게 배울 것이라 보면 됩니다.

'Electronics > Electronic circuit' 카테고리의 다른 글

| 회로이론 - 인덕터(inductor) (0) | 2020.04.01 |

|---|---|

| 회로이론 - 커패시터(capacitor) (0) | 2020.04.01 |

| 회로이론 - superposition(중첩) (1) | 2020.03.31 |

| 회로이론 - maximum power transfer (0) | 2020.03.31 |

| 회로이론 - 등가회로(Equivalent circuit) (0) | 2020.03.31 |